SLUS644B - FEBRUARY 2005 - MAY 2005

## **DUAL SLOT PCI-X 2.0 HOT-PLUG POWER CONTROLLER**

#### **FEATURES**

- Supports PCI, PCI-X 1.0 and PCI-X 2.0 Slots

- Internal Power Switches for –12 V, 12 V, 3.3 V Aux

- Control for Power FETs for 5 V, 3.3 V, and VIO

- Overload Protection on All Supplies

- Current Regulation on 3.3 V, 5 V and VIO Supplies

- Soft Start to Minimize Inrush Current

- Programmable Slew Rate for 3.3 V, 5 V, 12 V, VIO and Vaux Supplies

- Direct Control of All Functions

- VIO Selection Based on Card Type

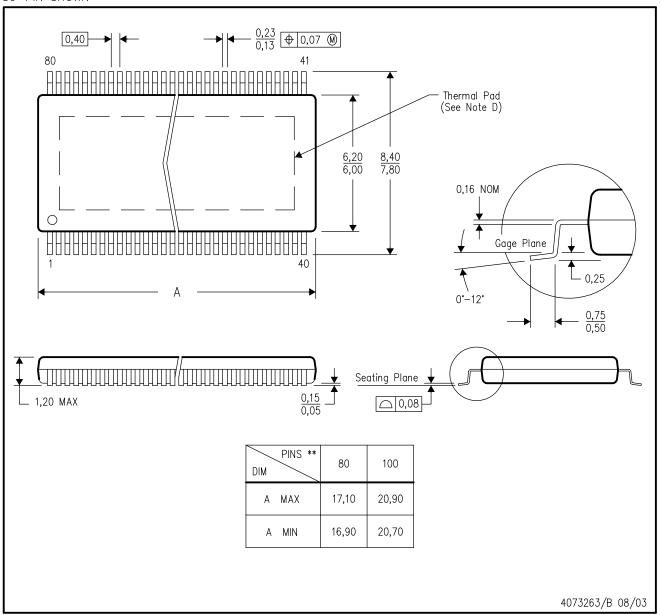

- 80-Lead PowerPad™ HTSSOP Package

- Narrow Package that Fits Between PCI Slots

#### **APPLICATIONS**

Hot Plug Slots in Servers

#### DESCRIPTION

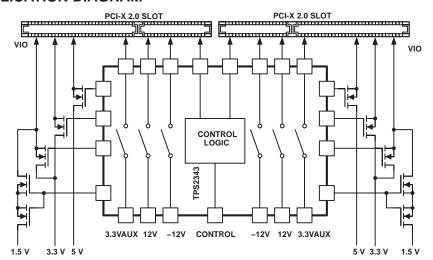

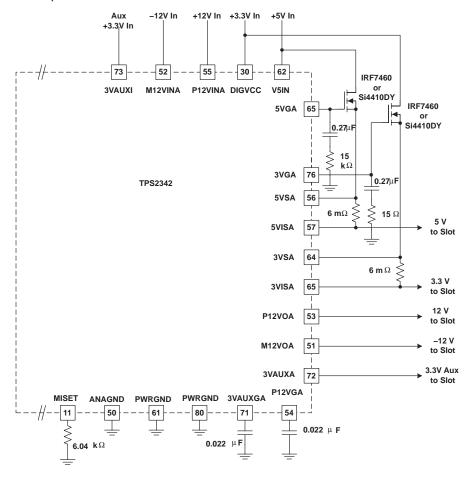

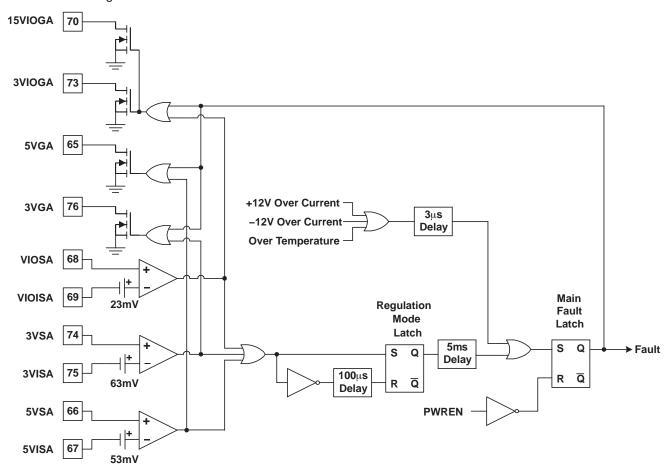

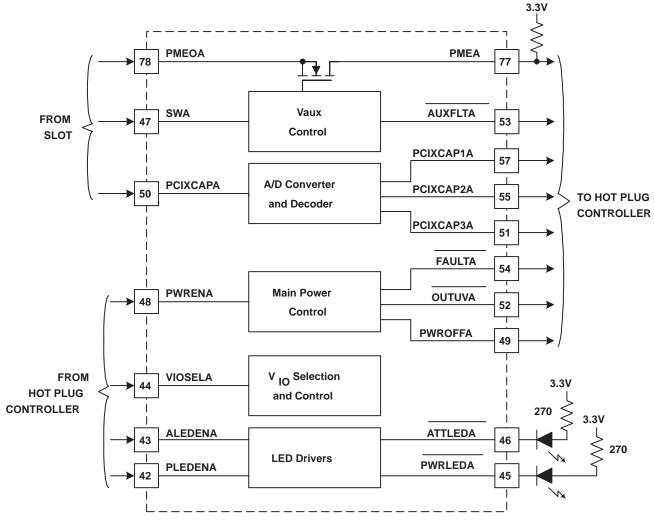

Each TPS2343 contains main supply power control, auxiliary supply power control, power FETs for 12-V, -12-V and auxiliary 3.3-V supplies, VIO control, and digital control for two slots.

The main power control circuits start with all supplies off and all outputs are held off until PGOOD is asserted, indicating that system supplies are valid. Then, when power enable is asserted, the control circuit applies constant current to the gates of the power FETs, allowing each FET to ramp load voltage linearly. Each supply can be programmed for a desired ramp rate by selecting the appropriate gate capacitor. The TPS2343 monitors load current and regulates peak current to prevent disturbances to the system power rails. If load current remains regulated for longer than 5 ms, that slot is latched off

Logic inputs to the TPS2343 access all functions of the TPS2343. All status information from the TPS2343 is available on logic outputs.

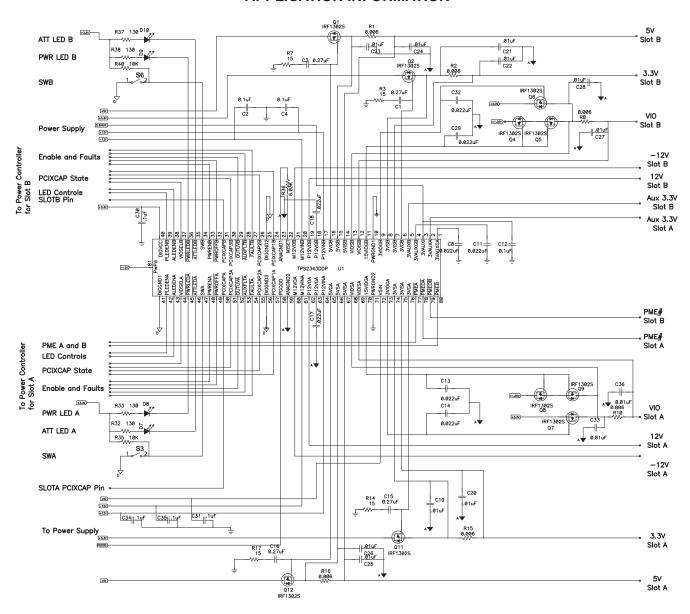

#### SIMPLIFIED APPLICATION DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPad™ is a trademark of Texas Instruments Incorporated.

## **DESCRIPTION (CONT.)**

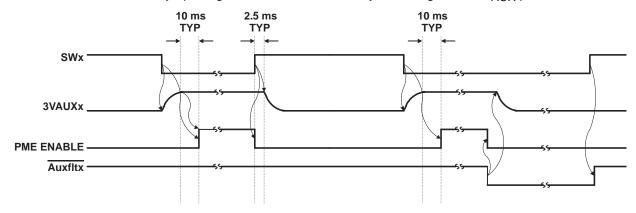

Auxiliary power control circuits switch, ramp, and monitor 3.3-V auxiliary power to each slot and control data switches that connect slot power management event (PME) outputs to the main PME bus after auxiliary supply is ramped. PME is disconnected when a board is turned off or a fault occurs on the board's auxiliary power. A fault on auxiliary power also shuts off main power to that board.

VIO control consists of gate drivers to select between 3.3 V and 1.5 V in response to command and current limiting circuitry to shut down a slot in the event of over current. Each TPS2343 contains power FETs for 12 V, –12 V, and auxiliary 3.3 V for two slots. These power FETs are short-circuit protected, slew rate controlled, and over-temperature protected.

The TPS2343 includes novel current limiting circuitry that limits instantaneous peak current and only shuts off the slot if the current remains out of spec for an extended time.

#### ORDERING INFORMATION

| T <sub>A</sub> | PACKAGE <sup>(1)</sup> |

|----------------|------------------------|

| 'A             | HTSSOP (DDP)           |

| -40°C to +85°C | TPS2343DDP             |

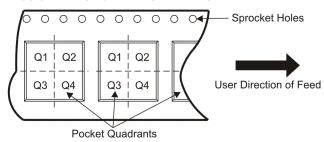

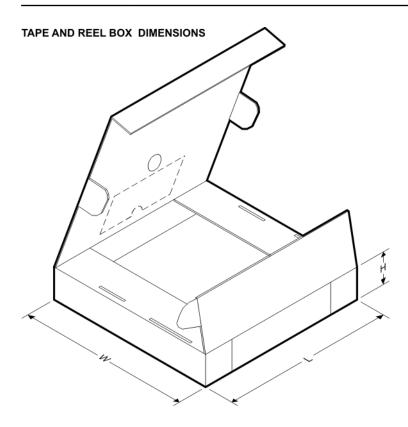

<sup>(1)</sup> Add suffix R to device type (e.g. TPS2343DDPR) to specify taped and reeled.

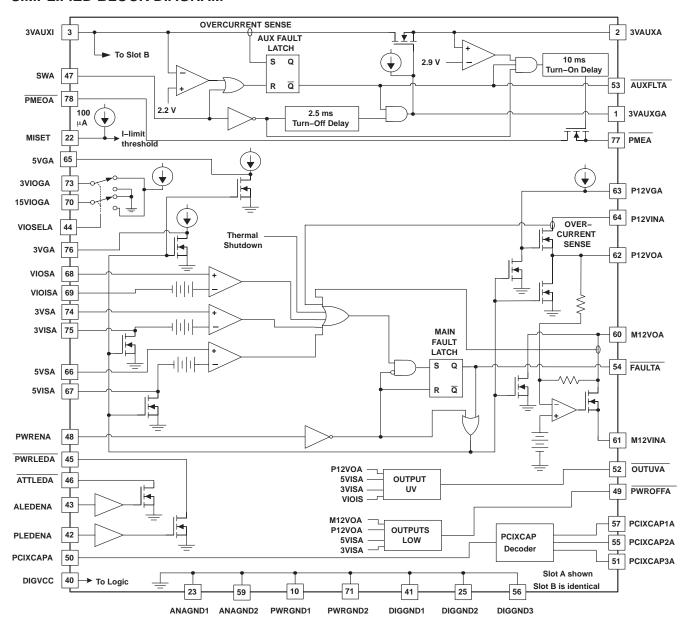

## SIMPLIFIED BLOCK DIAGRAM

In this drawing, circuits related to many functions are oversimplified. See the Application Section of the data sheet for a more detailed representations of these functions.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)†‡

| PARAMETER                                                              | TPS2343                           | UNIT |

|------------------------------------------------------------------------|-----------------------------------|------|

| Input voltage range, P12VIN                                            | -0.5 to 15                        |      |

| M12VIN                                                                 | -15.0 to 0.5                      |      |

| All others                                                             | -0.5 to 7                         | .,   |

| Output voltage range, P12VO, 5VG, 3VG, 15VIOG, 3VIOG                   | -0.5 to V <sub>P12VIN</sub> + 0.5 | V    |

| P12VG                                                                  | -0.5 to 28                        |      |

| M12VO                                                                  | -15 to 0.5                        |      |

| Output current, FAULT, OUTUV, PWROFF                                   | 50                                | mA   |

| Output current pulse, P12VO (dc internally limited)                    | 3                                 |      |

| M12VO                                                                  | 0.8                               | Α    |

| 3VAUX                                                                  | 2                                 |      |

| Operating junction temperature range, T <sub>J</sub>                   | -40 to 100                        |      |

| Storage temperature range, T <sub>Stg</sub>                            | -65 to 150                        | °C   |

| Lead temperature soldering 1.6 mm (1/16 inch) from case for 10 seconds | 260                               |      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to Absolute Maximum Rated conditions for extended periods may affect device reliability

# **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

| TEST METHOD                | MIN | UNIT |

|----------------------------|-----|------|

| Human body model (HBM)     | 2   | kV   |

| Charged device model (CDM) | 1   | kV   |

## RECOMMENDED OPERATING CONDITIONS

|               | PARAMETER                          | MIN   | TYP  | MAX   | UNIT |

|---------------|------------------------------------|-------|------|-------|------|

| Input supply, | M12VINA, M12VINB                   | -10.8 | -12  | -13.2 |      |

|               | P12VINA, P12VINB                   | 10.8  | 12   | 13.2  | .,   |

|               | DIGVCC, 3VAUXI                     | 3.0   | 3.3  | 3.6   | V    |

|               | V5IN                               | 4.75  | 5.00 | 5.25  |      |

| Load current, | PWRLEDA, PWRLEDB, ATTLEDA, ATTLEDB | 0     |      | 24    |      |

|               | P12VOA, P12VOB                     | 0     |      | 1100  |      |

|               | M12VOA, M12VOB                     | 0     |      | -100  | mA   |

|               | 3VAUXA, 3VAUXB                     | 0     |      | 375   |      |

## THERMAL SHUTDOWN

| PARAMETER                               | TYP | UNIT |

|-----------------------------------------|-----|------|

| Junction temperature shutdown           | 150 | °C   |

| Junction temperature – cooldown restart | 140 | °C   |

<sup>‡</sup> All voltages are with respect to DIGGND.

#### **DISSIPATION RATING TABLE**

| PACKAGE         | TA              | THERMAL RESISTANCE JUNCTION TO CASE $\Theta_{\mbox{\scriptsize JC}}$ | THERMAL RESISTANCE<br>JUNCTION TO AMBIENT<br>(NOTE 1) ⊝JA | THERMAL RESISTANCE JUNCTION TO AMBIENT (NOTE 2) ⊝JA |

|-----------------|-----------------|----------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------|

| HTSSOP-80 (DDP) | –40 °C to 85 °C | 1.4 °C/W                                                             | 23 °C/W                                                   | 32 °C/W                                             |

Note 1: Thermal resistance measured using an 8-layer PC board following the layout recommendations in TI Publication *PowerPAD Thermally Enhanced Package* Technical Brief SLMA002.

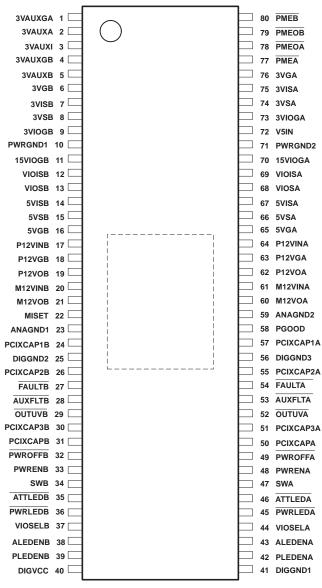

#### **SERIAL MODE PINOUT**

#### HTSSOP-80 DDP Package (Top View)

Note 2: Thermal resistance measured using an 8-layer PC board using only top PC board copper to spread the heat.

P12VIN = 12 V, DIGVCC = 3.3 V, M12VIN = -12 V, 3VAUXIN = 3.3 V, V5IN = 5 V, RMISET = 6.04 k $\Omega$ , all outputs unloaded, T<sub>A</sub> = -40°C to 85°C, (unless otherwise noted) (1)(2)(3)

# 5-V Main Supply

| PARAMETER                            | TEST CONDITIONS                   | MIN   | TYP   | MAX   | UNIT |

|--------------------------------------|-----------------------------------|-------|-------|-------|------|

| 5VS-5VIS overcurrent threshold (5 V) |                                   | 43    | 53    | 63    | mV   |

| 5VIS voltage fault threshold         |                                   | 4.25  | 4.5   | 4.75  | V    |

| 5VS input bias current               | PWREN = high                      | -100  |       | 100   |      |

| 5VIS input bias current              | PWREN = high                      | 100   | 250   | 400   | μΑ   |

| 5VIS bleed current                   | PWREN = low, 5VIS = 5V            | 8     | 60    |       | mA   |

| 5VG charge current                   | PWREN = high, 5VG = 5 V           | -70   | -100  | -130  | μΑ   |

| 5VG discharge resistance             | 0.1 V < V <sub>5</sub> VG < 0.5 V | 1.5   | 4     | 15    | Ω    |

| 5VG good threshold                   |                                   | 11    | 11.5  | 12    | V    |

| V5IN supply current                  |                                   |       | 2     | 6     | mA   |

| 5VIS low comparator threshold        | PWREN = low                       | 0.075 | 0.100 | 0.150 | V    |

# 3.3-V Main Supply

| PARAMETER                              | TEST CONDITIONS                  | MIN   | TYP   | MAX   | UNIT |

|----------------------------------------|----------------------------------|-------|-------|-------|------|

| 3VS-3VIS overcurrent threshold (3.3 V) |                                  | 48    | 63    | 76    | mV   |

| 3VIS voltage fault threshold           |                                  | 2.5   | 2.7   | 2.9   | V    |

| 3VS input bias current                 | PWREN = high                     | -100  |       | 100   |      |

| 3VIS input bias current                | PWREN = high                     | 100   | 290   | 400   | μΑ   |

| 3VIS bleed current                     | PWREN = low, 3VIS = 3.3 V        | 8     | 40    |       | mA   |

| 3VG charge current                     | PWREN = high, 3VG = 5 V          | -70   | -100  | -130  | μΑ   |

| 3VG discharge resistance               | 0.1 V < V <sub>3VG</sub> < 0.5 V | 1.5   | 4     | 15    | Ω    |

| DIGVCC supply current                  |                                  |       | 1.2   | 3     | mA   |

| 3VIS low comparator threshold          | PWREN = low                      | 0.075 | 0.100 | 0.150 | V    |

P12VIN = 12 V, DIGVCC = 3.3 V, M12VIN = -12 V, 3VAUXIN = 3.3 V, V5IN = 5 V, RMISET = 6.04 k $\Omega$ , all outputs unloaded,  $T_A = -40^{\circ}C$  to 85°C, (unless otherwise noted)  $^{(1)(2)(3)}$

## 12-V Main Supply

| PARAMETER                           | TEST CONDITIONS                                                       | MIN   | TYP   | MAX   | UNIT |

|-------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|------|

| 40 What and an link an analytic and | T <sub>A</sub> = T <sub>J</sub> = 25°C, P12VG > 18 V                  |       | 0.18  | 0.30  |      |

| 12-V internal switch on resistance  | $T_A = -40  ^{\circ}\text{C}$ to 85 $^{\circ}\text{C}$ , P12VG > 18 V |       |       | 0.4   | Ω    |

| 12-V overcurrent threshold          |                                                                       | 1.25  | 1.50  | 1.75  | Α    |

| P12VIN supply current, outputs off  | PWREN = low                                                           |       | 1.8   | 3     | mA   |

| P12VG gate good threshold           |                                                                       | 17.5  | 19.0  | 20.5  | V    |

| P12VO fault threshold               | After P12VG and 5V3VG good                                            | 9.75  | 10.15 | 10.45 |      |

| P12VG gate charge current           | PWREN = high                                                          | -5    | -10   | -20   | μΑ   |

| P12VG gate discharge resistance     | 0.1 V < V <sub>P12VG</sub> < 0.5V                                     | 1.5   | 4     | 15    | Ω    |

| <b>-</b>                            | PWREN = high to P12VO = 11.4 V,<br>CP12VG = 22 nF                     |       | 28    | 55    |      |

| Turn-on time                        | PWREN = high to P12VO = 11.4 V,<br>$C_{P12VG} = 0 \text{ nF}$         |       | 0.5   | 2.0   | ms   |

| Turn-off time                       | PWREN = low to P12VO low comparator trip, CP12VG = 22 nF              |       | 1.5   | 3.5   | μs   |

| P12VO bleed current                 | PWREN = low, P12VO = 12 V                                             | 8     | 20    |       | mA   |

| P12VO low comparator threshold      | PWREN = low                                                           | 0.075 | 0.100 | 0.150 | V    |

| P12VO turn-on slew rate             | C <sub>P12VG</sub> = 0 pF, 10% to 90% measurement                     | 2     |       | ·     | V/ms |

## -12-V Main Supply

| PARAMETER                              | TEST CONDITIONS                                                                                     | MIN    | TYP    | MAX    | UNIT |

|----------------------------------------|-----------------------------------------------------------------------------------------------------|--------|--------|--------|------|

| 40.11.                                 | $T_A = T_J = 25^{\circ}C$ , steady state                                                            |        | 0.50   | 0.75   |      |

| -12-V internal switch on-resistance    | internal switch on-resistance $T_A = -40  ^{\circ}\text{C}$ to 85 $^{\circ}\text{C}$ , steady state |        |        | 0.9    | Ω    |

| -12-V overcurrent threshold            |                                                                                                     | 0.15   | 0.20   | 0.25   | А    |

| M12VIN supply current, outputs off     | PWREN = low                                                                                         |        | 1000   | 2000   | μΑ   |

| M12VO turn-on slew rate <sup>(4)</sup> | C <sub>P12VG</sub> = 22 nF, 10% to 90% measurement                                                  | 0.30   | 0.68   | 1.10   | V/ms |

| Turn-on time                           | $C_{P12VG}$ = 22 nF, PWREN = high to M12VO = $-10.4$ V, $R_L$ = 120 $\Omega$                        | 12     | 18     | 37     | ms   |

| Turn-off time                          | PWREN = low to M12VO low comparator trip                                                            |        | 1.5    | 3.5    | μs   |

| M12VO bleed current                    | PWREN = low, M12VO = -12 V                                                                          | -8     | -20    |        | mA   |

| M12VO low comparator threshold         | PWREN = low                                                                                         | -0.075 | -0.100 | -0.150 | V    |

NOTES: (1). All voltages are with respect to DIGGND unless otherwise stated.

- (2) Currents are positive into and negative out of the specified terminal.

- (3) When references to lines of individual slots are given without the slot identifier, the statement applies to lines on each slot.

- (4) -12-V main supply turn on is controlled by the +12-V main supply turn on, so the -12-V main supply slew rate is a function of CP12VG.

P12VIN = 12 V, DIGVCC = 3.3 V, M12VIN = -12 V, 3VAUXIN = 3.3 V, V5IN = 5 V, RMISET = 6.04 k $\Omega$ , all outputs unloaded, T<sub>A</sub> = -40°C to 85°C, (unless otherwise noted) (1)(2)(3)

# **VIO** Supply

| PARAMETER                                            | TEST CONDITIONS                                                       | MIN   | TYP   | MAX   | UNIT |

|------------------------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|------|

| 15VG, 3VIOG output voltage high                      |                                                                       | 11.5  | 11.9  |       | V    |

| VIOS – VIOIS overcurrent threshold (1.5 V operation) |                                                                       | 20.0  | 23.5  | 27.0  | mV   |

| 15VIOG, 3VIOG turn-off resistance                    | PWREN = low, 0.1 V < V <sub>VIOG</sub> ,<br>V <sub>VIOG</sub> < 0.5 V | 10    | 50    | 100   | Ω    |

| VIOS input bias current                              | PWREN = high, VIOSEL = low, test circuit Figure 7                     | -100  | 20    | 100   |      |

| VIOIS input bias current                             | PWREN = high, VIOSEL = low, test circuit Figure 7                     | -100  | 20    | 200   | μΑ   |

| VIOIS bleed current                                  | PWREN = low, VIOIS =1.5 V                                             | 8     | 20    |       | mA   |

| VIOIS low comparator threshold                       | PWREN = low                                                           | 0.075 | 0.100 | 0.150 |      |

| VIOIS fault threshold                                |                                                                       | 1.275 | 1.325 | 1.375 | V    |

| 15VIOG low voltage                                   | PWREN = low                                                           |       | 0.1   | 1.0   |      |

| 15VIOG, 3VIOG gate charge current                    |                                                                       | 7     | 10    | 13    | μΑ   |

## **Power Fault Response**

| PARAMETER                             | TEST CONDITIONS   | MIN | TYP | MAX | UNIT |

|---------------------------------------|-------------------|-----|-----|-----|------|

| Overcurrent fault detection time      | 12 V              | 2   |     | 6.5 |      |

|                                       | −12 V, i = 250 mA | 4   |     | 12  | μs   |

| Overcurrent response time to regulate | 5 V, 3.3 V, Vio   |     | 1   | 3   |      |

| Overcurrent fault detection time      | 5 V, 3.3 V, Vio   | 3   |     | 8   | ms   |

| Overcurrent fault clearing time       | 5 V, 3.3 V, Vio   | 50  |     | 150 | μs   |

NOTES: (1) All voltages are with respect to DIGGND unless otherwise stated.

- (2) Currents are positive into and negative out of the specified terminal.

- (3) When references to lines of individual slots are given without the slot identifier, the statement applies to lines on each slot.

P12VIN = 12 V, DIGVCC = 3.3 V, M12VIN = -12 V, 3VAUXIN = 3.3 V, V5IN = 5 V, RMISET = 6.04 k $\Omega$ , all outputs unloaded, T<sub>A</sub> = -40°C to 85°C, (unless otherwise noted) (1)(2)(3)

## 3.3 VAUX and PME

| PARAMETER                                          | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------------------|------------------------------------------------------------------|------|------|------|------|

| 3VAUX overcurrent threshold                        |                                                                  | 0.8  | 1.1  | 1.45 | Α    |

| 3VAUXI to 3VAUX switch on resistance               | SW = low, 3VAUXG = 10 V                                          |      | 300  | 400  | mΩ   |

| 3VAUXI undervoltage threshold                      | SW = low                                                         | 1.9  | 2.2  | 2.9  | V    |

| 3VAUXI supply current, 3VAUX off                   | SW = high                                                        |      | 1000 | 2000 | ٨    |

| 3VAUXG turn-on current                             | SW = low, 3VAUXG = 3.3 V                                         | -3   | -5   | -7   | μΑ   |

| 3VAUXG turn-off resistance                         | SW = high, 0.1 V < 3VAUXG < 0.5 V                                | 3    | 8    | 30   | Ω    |

| 3VAUX turn-on time with no gate capacitor          | C <sub>3VAUXG</sub> = 0 pF, 10% to 90% measurement               |      | 200  | 350  | μs   |

| 3VAUX turn-on slew rate with gate capacitor        | C <sub>3VAUXG</sub> = 22 nF, 10% to 90% measurement              | 0.13 | 0.23 | 0.32 | V/ms |

| 3VAUX bleed current                                | SW = high, 3VAUX = 3.0 V                                         | 8    | 28   |      | mA   |

| 3VAUX turn-off time from SW                        | From SW > 2.0 V to 3VAUX < 0.5 V,<br>C <sub>3VAUXG</sub> = 22 nF |      | 1.2  | 5.0  | ms   |

| 3VAUX turn-off time from Fault                     | From 3VAUX overcurrent fault                                     |      | 17   | 25   | μs   |

| PME turn-on time from 3VAUX                        | From 3VAUX > 3.0 V, $C_{3VAUX} = 150 \mu F$                      | 6    | 10   | 17   | ms   |

| PME turn-off time from SW                          | From SW > 2.0 V                                                  |      |      | 4    | _    |

| PME turn-off time from Fault                       | From 3VAUX overcurrent fault                                     |      |      | 4    | μs   |

| PME switch on resistance                           | SW = low                                                         |      | 10   | 20   | Ω    |

| 3VAUX output rising threshold to PME switch closed |                                                                  | 2.5  |      | 3.0  | V    |

# **DC Logic Characteristics**

| PARAMETER                                     | TEST CONDITIONS                                          | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------------------|----------------------------------------------------------|------|------|------|------|

| Input high voltage (all digital inputs)       |                                                          | 2.0  |      |      |      |

| Input low voltage (all digital inputs)        |                                                          |      |      | 0.8  |      |

| Input hysteresis (PGOOD)                      |                                                          | 0.15 |      | 0.60 |      |

| Output high voltage (all push-pull outputs)   | I <sub>L</sub> = 4 mA                                    | 2.4  | 2.8  |      | V    |

| Cotoot Issue (ATTLED DIMPLED)                 | I <sub>L</sub> = 8 mA                                    |      |      | 0.5  |      |

| Output low voltage (ATTLED, PWRLED)           | I <sub>L</sub> = 24 mA                                   |      | 0.4  | 0.8  |      |

| Output low voltage (all other outputs)        | I <sub>L</sub> = 4 mA                                    |      | 0.2  | 0.5  |      |

| Input pull-up resistor impedance              | For inputs with pull-up resistors (see pin descriptions) | 30   |      | 200  | kΩ   |

| PCIXCAP threshold between 33 MHz and 533 MHz  |                                                          | 0.3  | 0.4  | 0.5  |      |

| PCIXCAP threshold between 533 MHz and 266 MHz |                                                          | 1.1  | 1.2  | 1.3  | .,   |

| PCIXCAP threshold between 266 MHz and 66 MHz  |                                                          | 1.95 | 2.05 | 2.15 | V    |

| PCIXCAP threshold between 66 MHz and 133 MHz  |                                                          | 2.8  | 2.9  | 3.0  |      |

- NOTES: (1). All voltages are with respect to DIGGND unless otherwise stated.

- (2) Currents are positive into and negative out of the specified terminal.

- (3) When references to lines of individual slots are given without the slot identifier, the statement applies to lines on each slot.

| TERMINAL |         |     |                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER   | NAME    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                   |

| 1        | 3VAUXGA | I/O | This pin is connected to the gate of the slot A 3VAUX internal power FET. Connect a capacitor from this pin to PWRGND to program the slot A 3VAUX ramp rate. The recommended capacitor value is 22 nF for 0.23 V/ms ramp rate.                                                                                                                                                                |

| 2        | 3VAUXA  | 0   | This output supplies 3VAUX power to slot A when enabled and is pulled low by an internal FET when there is a fault on slot A 3VAUX or when SWA is opened.                                                                                                                                                                                                                                     |

| 3        | 3VAUXI  | I   | Connect this power input to 3.3 V power to drive 3VAUX loads. Connect a 0.1-μF capacitor from this pin to PWRGND.                                                                                                                                                                                                                                                                             |

| 4        | 3VAUXGB | I/O | This pin is connected to the gate of the slot B 3VAUX internal power FET. Connect a capacitor from this pin to PWRGND to program the slot B 3VAUX ramp rate. The recommended capacitor value is 22 nF for 0.23 V/ms ramp rate.                                                                                                                                                                |

| 5        | 3VAUXB  | 0   | This output supplies 3VAUX power to slot B when enabled and is pulled low by an internal FET when there is a fault on slot B 3VAUX or when SWB is opened.                                                                                                                                                                                                                                     |

| 6        | 3VGB    | I/O | Gate drive for the 3-V slot B FET switch. Ramp rate is programmed by an external capacitor in series with a 15-k $\Omega$ resistor connected from this pin to PWRGND. A capacitor value of 270 nF sets 0.37 V/ms ramp rate.                                                                                                                                                                   |

| 7        | 3VISB   | I   | This pin in conjunction with the 3VSB pin senses the current to the 3.3-V slot B. It connects to the load side of the 3.3-V current sense resistor. The recommended current sense resistor value is 6 m $\Omega$ . When PWRENB is false or FAULTB is true, this pin is discharged to PWRGND by an internal FET. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended.             |

| 8        | 3VSB    | I   | This pin in conjunction with the 3VISB pin senses the current to the 3.3-V slot B main power load. Connect to the source of the 3.3-V FET switch. A $0.01$ - $\mu$ F capacitor from this pin to ANAGND is recommended.                                                                                                                                                                        |

| 9        | 3VIOGB  | I/O | Gate drive for the 3.3-V V <sub>IO</sub> slot B FET switches. Ramp rate is programmed by the external capacitor connected from 3VIOGB to PWRGND. The recommended capacitor value is 22 nF for a 0.45 V/ms ramp rate.                                                                                                                                                                          |

| 10       | PWRGND1 | GND | Ground for high-current paths including discharge current of external gate capacitors.                                                                                                                                                                                                                                                                                                        |

| 11       | 15VIOGB | I/O | Gate drive for the 1.5-V V <sub>IO</sub> slot B FET switches. Ramp rate is programmed by the external capacitor connected from 15VIOGB to PWRGND. The recommended capacitor value is 22 nF for a 0.45 V/ms ramp rate.                                                                                                                                                                         |

| 12       | VIOISB  | I   | This pin in conjunction with the VIOSB pin senses the current to $V_{IO}$ slot B. It connects to the load side of the $V_{IO}$ current sense resistor. The recommended current sense resistor value is 6 m $\Omega$ . When PWRENB is false or FAULTB is true, this pin is discharged to PWRGND by an internal FET. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended.          |

| 13       | VIOSB   | I   | This pin in conjunction with the VIOISB pin senses the current to $V_{IO}$ slot B. Connect to the current sense resistor at the Vio FET switch. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended.                                                                                                                                                                             |

| 14       | 5VISB   | I   | This pin in conjunction with the 5VSB pin senses the current to the 5-V slot B main power load. It connects to the load side of the 5-V current sense resistor. The recommended current sense resistor value is 6 m $\Omega$ . When PWRENB is false or FAULTB is true, this pin is discharged to PWRGND by an internal FET. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended. |

| 15       | 5VSB    | I   | This pin in conjunction with the 5VISB pin senses the current to the 5-V slot B main power load. It connects to the source of the 5-V FET switch. A $0.01$ - $\mu$ F capacitor from this pin to ANAGND is recommended.                                                                                                                                                                        |

| 16       | 5VGB    | I/O | Gate drive for the 5-V slot B FET switch. Ramp rate is programmed by an external capacitor in series with a 15-k $\Omega$ resistor connected from this pin to PWRGND. A capacitor value of 270 nF sets 0.37 V/ms ramp rate.                                                                                                                                                                   |

| 17       | P12VINB | I   | The 12-V power input to slot B. This input must be connected to P12VINA. Connect a $0.1$ - $\mu F$ capacitor from this pin to PWRGND.                                                                                                                                                                                                                                                         |

| 18       | P12VGB  | I/O | This pin is connected to the gate of the slot B 12-V internal power FET. Connect a capacitor from this pin to PWRGND to program the slot B 12-V and –12-V power ramp rate. The recommended capacitor value is 22 nF for 0.45 V/ms ramp rate on 12 V and a 0.68 V/ms ramp rate on –12-V power.                                                                                                 |

| TERMINAL |           |     |                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER   | NAME      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                        |

| 19       | P12VOB    | 0   | This output delivers 12-V power to slot B when enabled and is pulled to PWRGND by an internal FET when PWRRNB is false or FAULTB is true.                                                                                                                                                                                                                                          |

| 20       | M12VINB   | I   | Connect this power input to $-12$ -V power to drive slot B. This input must be connected to M12VINA. Connect a $0.1$ - $\mu$ F capacitor from this pin to PWRGND.                                                                                                                                                                                                                  |

| 21       | M12VOB    | 0   | This output delivers –12-V powe <u>r to slot B</u> when enabled and is pulled to PWRGND by an internal FET when PWRRNB is false or FAULTB is true. Turn-on of –12-V power tracks turn-on of 12-V power and is controlled by the capacitor on P12VGB.                                                                                                                               |

| 22       | MISET     | I/O | This pin programs current limit for 12-V, 5-V, 3.3-V, and $-12$ -V main supplies. MISET does not control 3.3VAUX or V $_{1O}$ current limit. The recommended resistor from MISET to ANAGND is 6.04 k $_{10}$ ±1%. Increasing the value of this resistor raises the current-limit thresholds for the supplies listed above proportionately. MISET resistor is 12 k $_{10}$ maximum. |

| 23       | ANAGND1   | GND | Ground for low-level signals including the current sense circuits and the voltage reference.                                                                                                                                                                                                                                                                                       |

| 24       | PCIXCAP1B | 0   | This pin indicates bit 1 of the PCIXCAPB state.                                                                                                                                                                                                                                                                                                                                    |

| 25       | DIGGND2   | GND | This pin is the ground return for the digital circuits in the TPS2343.                                                                                                                                                                                                                                                                                                             |

| 26       | PCIXCAP2B | 0   | This pin indicates bit 2 of the PCIXCAPB state.                                                                                                                                                                                                                                                                                                                                    |

| 27       | FAULTB    | 0   | This is an open-drain output that is low if there is a fault on the main power to slot B. This pin has an internal 100-k $\Omega$ pull-up resistor to DIGVCC.                                                                                                                                                                                                                      |

| 28       | AUXFLTB   | 0   | This open-drain output is low if there is a fault on $V_{AUX}$ power to slot B. This pin has an internal 100-k $\Omega$ pull-up resistor to DIGVCC and hysteresis.                                                                                                                                                                                                                 |

| 29       | OUTUVB    | 0   | This open-drain output is low if slot B outputs are below normal operating range. This pin has an internal $100-k\Omega$ pull-up resistor to DIGVCC.                                                                                                                                                                                                                               |

| 30       | PCIXCAP3B | 0   | This pin indicates bit 3 of the PCIXCAPB state.                                                                                                                                                                                                                                                                                                                                    |

| 31       | PCIXCAPB  | 1   | This pin is the input to a 5-level A/D converter that determines the speed and mode of the inserted B slot card based on the impedance from this pin to ANAGND. The operation of this pin meets the specifications of the PCI–X Local Bus Specification, revision 2.0.                                                                                                             |

| 32       | PWROFFB   | 0   | This output is low when all of the slot B power outputs are discharged.                                                                                                                                                                                                                                                                                                            |

| 33       | PWRENB    | I   | This pin enables main power for slot B when high. This pin has an internal 100-kΩ pull-up resistor to DIGVCC and hysteresis. When low, FAULTB is clearded and OUTUVB is asserted.                                                                                                                                                                                                  |

| 34       | SWB       | I   | This input enables 3.3-V $V_{AUX}$ power to slot B. When low, $\overline{AUXFLTB}$ is cleared. This pin has an internal 100-k $\Omega$ pull-up resistor to 3VAUXI and hysteresis.                                                                                                                                                                                                  |

| 35       | ATTLEDB   | 0   | This output is an open-drain power output that directly drives the slot B attention indicator LED. This pin indicates the slot B LED attention indicator output signal from ALEDENB. This signal pulls low with up to 24 mA of drive when asserted and is pulled high by an on-chip 100-k $\Omega$ resistor to V5IN when deasserted.                                               |

| 36       | PWRLEDB   | 0   | This open-drain active-low power output directly drives the slot B power indicator LED. This pin indicates the slot B power LED output from PLEDENB. This signal pulls low with up to 24 mA of drive when asserted and is pulled high by an on-chip $100\text{-}k\Omega$ resistor to V5IN when deasserted.                                                                         |

| 37       | VIOSELB   | I   | This pin selects 3.3 V V <sub>IO</sub> for slot B when high, 1.5 V when low.                                                                                                                                                                                                                                                                                                       |

| 38       | ALEDENB   | - 1 | This pin controls ATTLEDB. When this input is high, the LED is on (low).                                                                                                                                                                                                                                                                                                           |

| 39       | PLEDENB   | I   | This pin controls PWRLEDB. When this input is high, the LED is on (low).                                                                                                                                                                                                                                                                                                           |

| 40       | DIGVCC    | I   | This pin is the 3.3-V main power input to the TPS2343. Bypass this pin to DIGGND with a $0.1$ - $\mu$ F ceramic capacitor close to the TPS2343.                                                                                                                                                                                                                                    |

| 41       | DIGGND1   | GND | This pin is the ground return for the digital circuits in the TPS2343.                                                                                                                                                                                                                                                                                                             |

| TE     | TERMINAL  |     | TERMINAL                                                                                                                                                                                                                                                                                                               |  |  |

|--------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER | NAME      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                            |  |  |

| 42     | PLEDENA   | 1   | This pin controls PWRLEDA. When this input is high, the LED is on (low).                                                                                                                                                                                                                                               |  |  |

| 43     | ALEDENA   | I   | This pin controls ATTLEDA. When this input is high, the LED is on (low).                                                                                                                                                                                                                                               |  |  |

| 44     | VIOSELA   | Ţ   | This pin selects 3.3 V V <sub>IO</sub> for slot A when high, 1.5 V when low.                                                                                                                                                                                                                                           |  |  |

| 45     | PWRLEDA   | 0   | This output is an open–drain active–low power output that directly drives the slot A power indicator LED. This pin indicates the slot A power LED output from PLEDENA. This signal pulls low with up to 24 mA of drive when asserted and is pulled high by an on-chip 100-k $\Omega$ resistor to V5IN when deasserted. |  |  |

| 46     | ATTLEDA   | 0   | This open-drain power output directly drives the slot A attention indicator LED. This pin indicates the slot A LED attention indicator output signal from ALEDENA. This signal pulls low with up to 24 mA of drive when asserted and is pulled high by an on-chip 100-k $\Omega$ resistor to V5IN when deasserted.     |  |  |

| 47     | SWA       | I   | This input enables 3.3-V Aux power to slot A. When low, $\overline{\text{AUXFLTA}}$ is cleared. This pin has an internal $100\text{-k}\Omega$ pull-up resistor to 3VAUXI and hysteresis.                                                                                                                               |  |  |

| 48     | PWRENA    | I   | This pin enables main power for slot A when high. When low, $\overline{\text{FAULTA}}$ is cleared and $\overline{\text{OUTUVA}}$ is asserted. This pin has an internal 100-k $\Omega$ pull-up resistor to DIGVCC and hysteresis.                                                                                       |  |  |

| 49     | PWROFFA   | 0   | This output is low when all of the slot A power outputs are discharged.                                                                                                                                                                                                                                                |  |  |

| 50     | PCIXCAPA  | -   | This pin is the input to a 5-level A/D converter that determines the speed and mode of the inserted A slot card based on the impedance from this pin to ANAGND. The operation of this pin meets the specifications of the PCI–X Local Bus Specification, revision 2.0.                                                 |  |  |

| 51     | PCIXCAP3A | 0   | This pin indicates bit 3 of the PCIXCAPA state.                                                                                                                                                                                                                                                                        |  |  |

| 52     | OUTUVA    | 0   | This open–drain output is low if slot A main outputs are below normal operating range. This pin has an internal 100- $k\Omega$ pull-up resistor to DIGVCC.                                                                                                                                                             |  |  |

| 53     | AUXFLTA   | 0   | This is an open-drain output that is low if there is a fault on $V_{AUX}$ power to slot A. This pin has an internal 100-k $\Omega$ pull-up resistor to DIGVCC.                                                                                                                                                         |  |  |

| 54     | FAULTA    | 0   | This is an open-drain output that is low if there is a fault on the main power to slot A. This pin has an internal 100-k $\Omega$ pull-up resistor to DIGVCC.                                                                                                                                                          |  |  |

| 55     | PCIXCAP2A | 0   | This pin indicates bit 2 of the PCIXCAPA state.                                                                                                                                                                                                                                                                        |  |  |

| 56     | DIGGND3   | GND | This pin is the ground return for the digital circuits in the TPS2343.                                                                                                                                                                                                                                                 |  |  |

| 57     | PCIXCAP1A | 0   | This pin indicates bit 1 of the PCIXCAPA state.                                                                                                                                                                                                                                                                        |  |  |

| 58     | PGOOD     | I   | This input is asserted when power is good in the whole system. This pin has an internal 100-k $\Omega$ pull-up resistor to DIGVCC and hysteresis.                                                                                                                                                                      |  |  |

| 59     | ANAGND2   | GND | Ground for low-level signals including the current sense circuits and the voltage reference.                                                                                                                                                                                                                           |  |  |

| 60     | M12VOA    | 0   | This output delivers –12-V powe <u>r to slot</u> A when enabled and is pulled to PWRGND by an internal FET when PWRENA is false or FAULTA is true. Turn-on of –12-V power tracks turn-on of 12-V power and is controlled by the capacitor on P12VGA.                                                                   |  |  |

| 61     | M12VINA   | I   | Connect this power input to -12-V power to drive slot A. This input must be connected to M12VINB. Connect a 0.1-µF capacitor from this pin to PWRGND.                                                                                                                                                                  |  |  |

| 62     | P12VOA    | 0   | This output delivers 12-V power to slot A when enabled and is pulled to PWRGND by an internal FET when PWRENA is false or FAULTA is true.                                                                                                                                                                              |  |  |

| TERMINAL |         |     | D. T. CODID TION                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER   | NAME    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 63       | P12VGA  | I/O | This pin is connected to the gate of the slot A 12-V internal power FET. Connect a capacitor from this pin to PWRGND to program the slot A 12-V and –12-V power ramp rate. The recommended capacitor value is 22 nF for 0.45-V/ms ramp rate on 12 V and a 0.68-V/ms ramp rate on –12-V power.                                                                                     |  |  |

| 64       | P12VINA | I   | The 12-V power input to slot A. This input must be connected to P12VINB. Connect a $0.1$ - $\mu F$ capacitor from this pin to PWRGND.                                                                                                                                                                                                                                             |  |  |

| 65       | 5VGA    | I/O | Gate drive for the 5-V slot A FET switch. Ramp rate is programmed by an external capacitor in series with a 15- $\Omega$ resistor connected from this pin to PWRGND. A capacitor value of 270 nF sets 0.37-V/ms ramp rate.                                                                                                                                                        |  |  |

| 66       | 5VSA    | I   | This pin in conjunction with the 5VISA pin senses the current to the 5-V slot A. It connects to the source of the 5-V FET switch. A $0.01$ - $\mu$ F capacitor from this pin to ANAGND is recommended.                                                                                                                                                                            |  |  |

| 67       | 5VISA   | I   | This pin in conjunction with the 5VSA pin senses the current to the 5-V slot A. It connects to the load side of the 5-V current sense resistor. The recommended current sense resistor value is $6m\Omega$ . When PWRENA is false or FAULTA is true, this pin is discharged to PWRGND by an internal FET. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended.       |  |  |

| 68       | VIOSA   | -   | This pin in conjunction with the VIOISA pin senses the current to $V_{\text{IO}}$ slot A. Connect to the current sense resistor at the Vio FET switch. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended.                                                                                                                                                          |  |  |

| 69       | VIOISA  | ı   | This pin in conjunction with the VIOSA pin senses the current to $V_{IO}$ slot A. It connects to the load side of the $V_{IO}$ current sense resistor. The recommended current sense resistor value is 6 m $\Omega$ . $V_{IO}$ bleed is connected to this pin. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended.                                                  |  |  |

| 70       | 15VIOGA | I/O | Gate drive for the 1.5-V V <sub>IO</sub> slot A FET switches. Ramp rate is programmed by the external capacitor connected from 15VIOGA to PWRGND. The recommended capacitor value is 22 nF for a 0.45-V/ms ramp rate.                                                                                                                                                             |  |  |

| 71       | PWRGND2 | GND | Ground for high-current paths including discharge current of external gate capacitors.                                                                                                                                                                                                                                                                                            |  |  |

| 72       | V5IN    | I   | Connect this power input to 5-V power. This input is used to bias analog circuits. Connect a $0.1$ - $\mu$ F capacitor from this pin to PWRGND.                                                                                                                                                                                                                                   |  |  |

| 73       | 3VIOGA  | I/O | Gate drive for the 3.3-V $V_{\text{IO}}$ slot A FET switches. Ramp rate is programmed by the external capacitor connected from 3VIOGA to PWRGND. The recommended capacitor value is 22 nF for a 0.45-V/ms ramp rate.                                                                                                                                                              |  |  |

| 74       | 3VSA    | ı   | This pin in conjunction with the 3VISA pin senses the current to the 3.3-V slot A main power load. Connect to the source of the 3.3-V FET switch. A 0.01-µF capacitor from this pin to ANAGND is recommended.                                                                                                                                                                     |  |  |

| 75       | 3VISA   | ı   | This pin in conjunction with the 3VSA pin senses the current to the 3.3-V slot A. It connects to the load side of the 3.3-V current sense resistor. The recommended current sense resistor value is 6 m $\Omega$ . When PWRENA is false or FAULTA is true, this pin is discharged to PWRGND by an internal FET. A 0.01- $\mu$ F capacitor from this pin to ANAGND is recommended. |  |  |

| 76       | 3VGA    | I/O | Gate drive for the 3.3-V slot A FET switch. Ramp rate is programmed by an external capacitor in series with a 15-k $\Omega$ resistor connected from this pin to PWRGND. A capacitor value of 270 nF sets 0.37-V/ms ramp rate.                                                                                                                                                     |  |  |

| 77       | PMEA    | I   | This input connects to the slot A power management event (PME) signal. This pin is internally pulled up to 3VAUXA with a $100-k\Omega$ resistor.                                                                                                                                                                                                                                  |  |  |

| 78       | PMEOA   | 0   | This output is connected to PMEA by a bus switch that is closed after slot A 3VAUX voltage is good and opens immediately when there is a fault on slot A 3VAUX or SWA opens.                                                                                                                                                                                                      |  |  |

| 79       | PMEOB   | 0   | This output is connected to PMEB by a bus switch that is closed after slot B 3VAUX voltage is good and opens immediately when there is a fault on slot B 3VAUX or SWB opens.                                                                                                                                                                                                      |  |  |

| 80       | PMEB    | I   | This input connects to the slot B power management event (PME) signal. This pin is internally pulled up to 3VAUXB with a $100-k\Omega$ resistor.                                                                                                                                                                                                                                  |  |  |

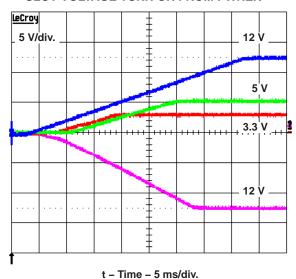

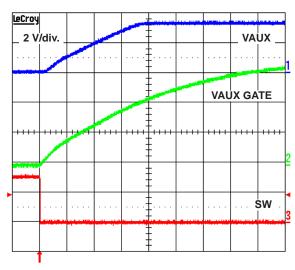

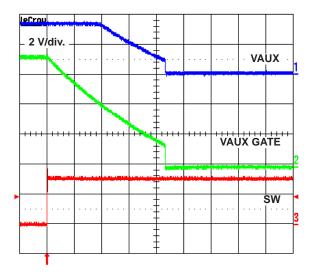

## **Turn-On Sequence**

Main power to the slot turns on when all input supplies are active and power is commanded, by asserting PWRENx. The charge pump combined with the P12VGx capacitor produces a linear voltage ramp on P12VGx, which produces a linear ramping of the 12-V output and the –12-V output. At the same time, a current source on 5VG combined with the 5VG capacitor produces a linear voltage ramp on 5VG and a current source on 3VG combined with the 3VG capacitor produces a linear voltage ramp on 3VG, which produces a linear ramping of the 3.3-V and 5-V main outputs.

During this time, if any main slot current exceeds the appropriate over-current threshold for more than the over-current sensitivity time, the slot latches off and remains off until the logic command is turned off and on again.

When P12VGx exceeds the 12-V gate good threshold, 5VG exceeds the 5-V good threshold, and 3VG exceeds the 3-V gate good threshold, outputs should be fully ramped and the power MOSFETs should be fully enhanced.

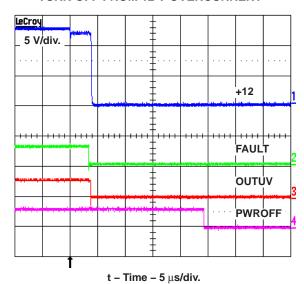

## +12-V Supply Control

The TPS2343 integrates an N-channel power MOSFET for the 12-V supply and a voltage multiplying charge pump to drive the gate of the power MOSFET to 20 V. Inrush current for the 12-V supply is controlled because the slew rate of the 12-V supply is limited. The slew rate for the 12-V supply is set by the capacitor from P12VG to AGND.

Slew rate can be estimated as:

$$\frac{dV}{dt} = \frac{I_{GATE}}{C_{P12VGx}}$$

where C<sub>P12VGx</sub> is the capacitor from P12VGx to AGND and I<sub>GATE</sub> is the P12VGx gate charge current.

PCI specifications allow for 12-V supply adapter card bulk capacitance of up to 300  $\mu$ F. This load capacitance causes additional inrush current of:

$$I_{INRUSH} = C_{LOAD} \times \frac{dV}{dt} = 300 \ \mu F \times \frac{I_{GATE}}{C_{P12VGx}}$$

Using the recommended value for  $C_{P12VGX}$  = 0.022  $\mu F$  and the typical value for  $I_{GATE}$  = 10  $\mu A$ , average inrush current can be estimated as:

$$I_{INRUSH} = 300 \ \mu F \times \frac{10 \ \mu A}{0.022 \ \mu F} = 0.136 \ A$$

An internal current–sense circuit monitors the 12-V supply. The over-current threshold for the 12-V supply is directly proportional to the resistor from MISET to AGND. Raising the MISET resistor simultaneously raises the current limit threshold for the 12-V, 5-V, 3.3-V and –12-V supplies. For example, to raise the nominal output current from the 12-V supply by 20%, increase the MISET resistor 20%. This resistor can be as high as 12 k $\Omega$  if necessary.

## -12-V Supply Control

The TPS2343 integrates an N-channel power MOSFET for the -12-V supply. This switch turns on when PWRENx is asserted and turns off when PWRENx is deasserted or when there is a fault on any main power supply to the slot.

Like the 12-V supply, inrush for the -12-V supply is controlled by controlling turn-on slew rate. The -12-V supply tracks the 12-V supply, so the slew rates of these supplies are directly related. To insure that the power MOSFET for the -12-V supply fully enhances, the tracking amplifier has a gain of approximately 1.4, producing a -12-V supply slew rate 40% higher than the 12-V supply slew rate.

PCI specifications allow for -12-V supply adapter card bulk capacitance of up to 150  $\mu$ F. This load capacitance causes additional inrush current of:

$$I_{INRUSH} = C_{LOAD} \times \frac{dV}{dt} = 150 \,\mu\text{F} \times \frac{I_{GATE}}{C_{P12VG}} \times 1.4$$

Using the recommended value for  $C_{P12VG}$  = 0.022  $\mu F$  and the typical value for  $I_{GATE}$  = 10  $\mu A$ , average inrush current can be estimated as:

$$I_{INRUSH} = 150 \,\mu\text{F} \times \frac{10 \,\mu\text{A}}{0.022 \,\mu\text{F}} \times 1.4 = 0.095 \,\text{A}$$

An internal current-sense circuit monitors the -12-V supply. The over-current threshold for the -12-V supply is directly proportional to the resistor from MISET to AGND. Raising the MISET resistor simultaneously raises the current limit threshold for the 12-V, 5-V, 3.3-V and -12-V supplies. For example, to raise the nominal output current from the -12-V supply by 20%, increase the MISET resistor 20%. This resistor can be as high as  $12\text{ k}\Omega$  if necessary.

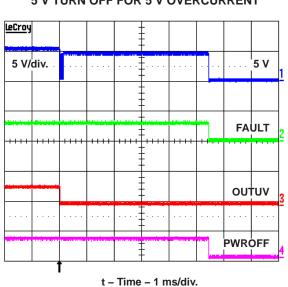

#### +5-V Main Supply Control

The TPS2343 uses external N-channel power MOSFETs for the 5-V supply. Inrush current for this supply is controlled because the slew rate of the supplies is limited. This slew rate is set by the capacitor from 5VGx to AGND. Slew rate can be estimated as:

$$\frac{dV}{dt} = \frac{I_{GATE}}{C_{5VG}}$$

where C<sub>5VG</sub> is the capacitor from 5VGx to AGND and I<sub>GATE</sub> is the 5VGx gate charge current.

PCI specifications allow for 5-V supply adapter card bulk capacitance of up to 3000  $\mu$ F. This load capacitance causes additional inrush current of:

$$I_{INRUSH} = C_{LOAD} \times \frac{dV}{dt} = 3000 \, \mu\text{F} \times \frac{I_{GATE}}{C_{5VGx}}$$

Using the recommended value for  $C_{5VGX}$  = 0.27  $\mu F$  and the typical value for  $I_{GATE}$  = 100  $\mu A$ , average inrush current can be estimated as:

$$I_{INRUSH} = 3000 \,\mu\text{F} \times \frac{100 \,\mu\text{A}}{0.27 \,\mu\text{F}} = 1.11 \,\text{A}$$

An external current-sense resistor monitors the 5-V supply. The calculation of external resistor values is shown in the determining component values section. The over-current thresholds is directly proportional to the resistor from MISET to AGND and inversely proportional to the current-sense resistor. Raising the MISET resistor simultaneously raises the current limit threshold for the 12-V, 5-V, 3.3-V and -12-V supplies. This resistor can be as high as  $12 \text{ k}\Omega$  if necessary.

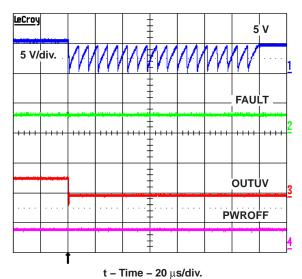

## +3.3-V Main Supply Control

The TPS2343 uses external N-channel power MOSFETs for the 3.3-V supply. Inrush current for this supply is controlled because the slew rate of the supply is limited. These slew rates are set by the capacitor from 3VGx to AGND. Slew rate can be estimated as:

$$\frac{dV}{dt} = \frac{I_{GATE}}{C_{3VGx}}$$

where C<sub>3VGx</sub> is the capacitor from 3VGx to AGND and I<sub>GATE</sub> is the 3VGx gate charge current.

PCI specifications allow for 3.3-V supply adapter card bulk capacitance of up to 3000  $\mu$ F. This load capacitance causes additional inrush current of:

$$I_{INRUSH} = C_{LOAD} \times \frac{dV}{dt} = 3000 \,\mu\text{F} \times \frac{I_{GATE}}{C_{3VGx}}$$

Using the recommended value for  $C_{3VGx}$  = 0.27  $\mu F$  and the typical value for  $I_{GATE}$  = 100  $\mu A$ , average inrush current can be estimated as:

$$I_{INRUSH} = 3000 \,\mu\text{F} \times \frac{100 \,\mu\text{A}}{0.27 \,\mu\text{F}} = 1.11 \,\text{A}$$

An external current-sense resistor monitors the 3.3-V supply. The calculation of external resistor values is shown in the determining component values section. The over-current threshold is directly proportional to the resistor from MISET to AGND and inversely proportional to the current-sense resistor. Raising the MISET resistor simultaneously raises the current limit threshold for the 12-V, 5-V, 3.3-V and -12-V supplies. This resistor can be as high as  $12 \text{ k}\Omega$  if necessary.

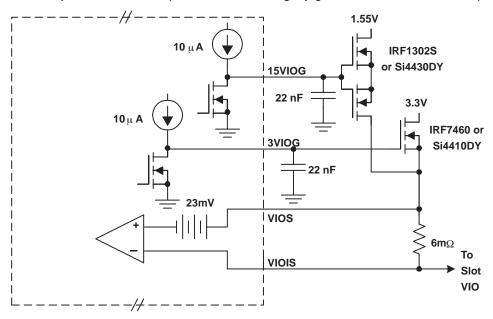

## +1.5-V and +3.3-V V<sub>IO</sub> Supply Control

$V_{IO}$  is frequently used to power  $V_{IO}$  for both the slot and the bridge so that there is minimal drop between the slot and the bridge  $V_{IO}$  supplies. When calculating the current-limit threshold for  $V_{IO}$ , take into account the current consumption of the slot and the bridge.

The TPS2343 uses external N-channel power MOSFETs for the 1.5-V and 3.3-V  $V_{IO}$  supplies. Inrush current for these supplies is controlled because the slew rate of the supplies are limited. Refer to the VIO Power Selection in the Application Section.

Both 1.5-V and 3.3-V VIO slew rates are usually set to the same value capacitor,  $C_{VIOGx}$  to AGND and on  $3_{VIOGx}$  to AGND.  $I_{GATE}$  is 10  $\mu$ A for both 15VIOGx and 3VIOGx. Slew rate can be estimated as:

$$\frac{\text{dV}}{\text{dt}} = \frac{I_{GATE}}{C_{VIOGx}}$$

PCI specifications allow for 1.5-V and 3.3-V  $V_{IO}$  supply adapter card bulk capacitance of up to 150  $\mu$ F. This load capacitance causes additional inrush current of:

$$I_{INRUSH} = C_{LOAD} \times \frac{dV}{dt} = 150 \ \mu F \times \frac{I_{GATE}}{C_{VIOGx}}$$

Using the recommended value for  $C_{VIOGx}$  = 0.022  $\mu F$  and the typical value for  $I_{GATE}$  = 5  $\mu A$ , average inrush current can be estimated as:

$$I_{INRUSH} = 150 \,\mu\text{F} \times \frac{10 \,\mu\text{A}}{0.022 \,\mu\text{F}} = 0.068 \text{A}$$

## **3VAUX Supply Control**

The TPS2343 3VAUX supply is completely independent of the main supply. Supply status and faults on main supplies have no effect on 3VAUX and faults on 3VAUX have no effect on main supply operation.

The TPS2343 uses internal power MOSFETs for the 3VAUX supply and voltage multiplying charge pumps to drive the gates of the power MOSFETs to 8 V. Inrush current for the 3VAUX supply is controlled because the slew rate of the 3VAUX supply is limited. This slew rate is set by the capacitor from 3VAUXGx to AGND. Slew rate can be estimated as:

$$\frac{\text{dV}}{\text{dt}} = \frac{I_{GATE}}{C_{3VAUXGx}}$$

where C<sub>3VAUXGx</sub> is the capacitor from 3VAUXGx to AGND and IGATE is the 3VAUXG gate charge current. Inrush current caused by this slewing and any adapter card load capacitance can be estimated as:

PCI specifications allow for 3.3VAUX supply adapter card bulk capacitance of up to 150  $\mu$ F. This load capacitance causes additional inrush current of:

$$I_{INRUSH} = C_{LOAD} \times \frac{dV}{dt} = C_{LOAD} \times \frac{5 \,\mu\text{A}}{C_{3VAUXGx}}$$

Using the recommended value for  $C_{3VAUXGx} = 0.022 \,\mu\text{F}$  and the typical value for  $I_{GATE} = 5 \,\mu\text{A}$ , average inrush current can be estamated as:

$$I_{RUSH} = 150 \,\mu\text{F} \times \frac{5 \,\mu\text{A}}{0.022 \,\mu\text{F}} = 0.034 \,\text{A}$$

The 3VAUXx current-sense threshold is internally set and can not be adjusted.

When main power is applied to the TPS2343, all gates are actively held low. When main power is removed, leakage current can potentially raise gate voltage, but because main power is not applied, no malfunction occurs. This is noted here as floating gates may be observed during bench testing, but this is not an application problem.

## **Layout Considerations**

It is important to use good layout practices regarding device placement and etch routing of the backplane/system board to optimize the performance of the hot plug circuit. Some of the key considerations are listed here:

- Decoupling capacitors should be located close to the device.

- Any protection devices (e.g. zener clamps) should be located close to the device.

- To reduce insertion loss across the hot plug interface, use wide traces for the supply and return current paths. A power plane can be used for the supply return or PWRGND nodes.

- Additional copper placed at the land patterns of the sense resistors and pass FETs can significantly reduce the thermal impedance of these devices, reducing temperature rise in the module and improving overall reliability.

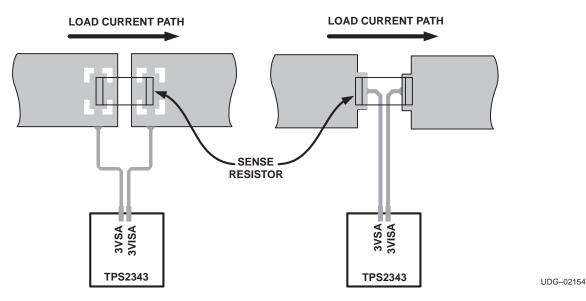

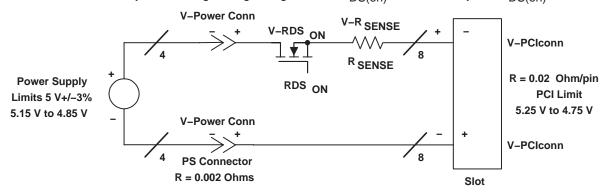

- Because typical values for current sense resistors can be very low (6 mΩ typical), board trace resistance between elements in the supply current paths becomes significant. To achieve maximum accuracy of the overload thresholds, good Kelvin connections to the resistors should be used for the current sense inputs to the device. The current sense traces should connect symmetrically to the sense resistor land pattern, in close proximity to the element leads, not upstream or downstream from the device.

Figure 1. Connecting the Sense Resistors

These recommended layouts provide force-and-sense (Kelvin) connection to the current sense resistor to minimize circuit board trace resistance.

## **Power and Grounding**

Connect all TPS2343 grounds directly to the digital ground plane on the circuit board through the shortest path possible. Also connect P12VINA, P12VINB, M12VINA and M12VINB directly to the appropriate power plane through the shortest path possible. A 0.1- $\mu$ F decoupling capacitor is recommended on each of these power pins, as close to the pin as possible.

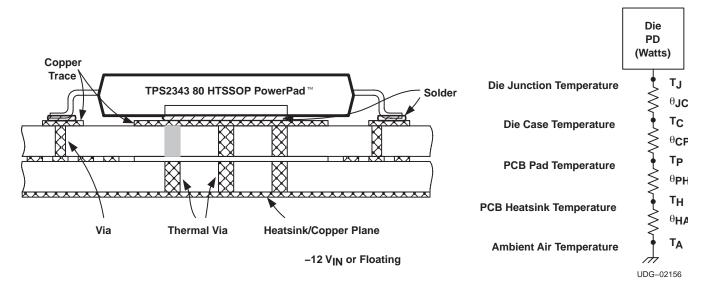

#### **Thermal Model**

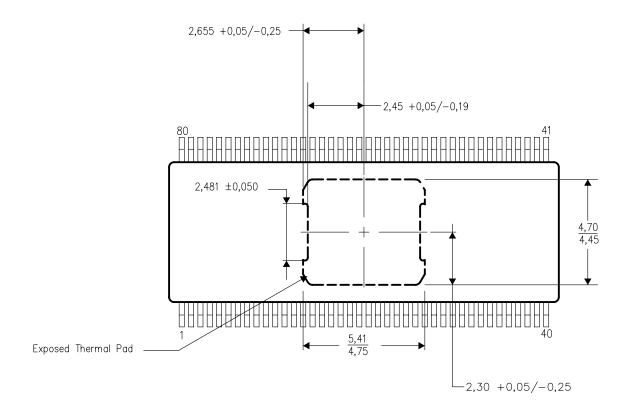

The TPS2343 is packaged in the HTSSOP-80 PowerPad™ small outline package. The PowerPad™ package is a thermally enhanced standard size device package designed to eliminate the use of bulky heatsinks and slugs traditionally used in thermal packages. This package can be easily mounted using standard printed circuit board (PCB) assembly techniques, and can be removed and replaced using standard repair procedures.

The leadframe die pad is exposed on the bottom of the device. This provides an extremely low thermal resistance between the die and the thermal pad. The thermal pad can be soldered directly to the PCB for heatsinking. In addition, through the use of thermal vias, the thermal pad can be directly connected to a power plane or special heat sink structure designed into the PCB. On the TPS2343, the die substrate is internally connected to the –12-V input supply. Therefore the power plane or heatsink connected to the thermal pad on the bottom of the device must also connect to the –12-V input supply (recommended) or float independent of any supply (acceptable).

The thermal performance can be modeled by determining the thermal resistance between the die and the ambient environment. Thermal resistances are measures of how effectively an object dissipates heat. Typically, the larger the device, the more surface area available for power dissipation and the lower the object's thermal resistance. Figure 3 illustrates the thermal path and resistances from the die, T<sub>J</sub> through the printed circuit board to the ambient air.

Figure 2. PowerPAD™ Thermal Model

Technical Brief *PowerPAD*™ *Thermally Enhanced Package* (SLMA002) can be used as a guide to model the TPS2343 thermal resistance.

# DDP PowerPad 80 Pin 4.70 6,20 6,00 7,10 16,90

NOTE:

centering.

The pad is centered in both directions with the pins. The tolerance includes both the size and the

When mounted to a copper pad with solder on a PCB with two ounce traces, the TPS2343 exhibits thermal resistance from junction to ambient of 29°C/W. When the TPS2343 is mounted to a conventional PCB with solder mask under the package and only the lead tips soldered to traces, the TPS2343 exhibits thermal resistance from junction to ambient of 35°C/W.

Refer to Technical Briefs: PowerPAD™ Thermally Enhanced Package SLMA003 and PowerPAD™ Made Easy SLMA004 for more information on using this PowerPad™ package.

## **Determining Component Values**

## **Load Conditions**

**Table 1. Load Conditions for Determining Component Values**

| SUPPLY DRIVER | I <sub>LOAD</sub> (A) | I <sub>TRIP</sub> (A) | C <sub>LOAD</sub><br>(μF) | SR<br>(V/s) |

|---------------|-----------------------|-----------------------|---------------------------|-------------|

| +12 V         | 0.500                 | 1.50                  | 300                       | 250         |

| +5 V          | 5.000                 | 7.00                  | 3000                      | 200         |

| +3.3 V        | 7.600                 | 10.0                  | 3000                      | 200         |

| -12 V         | 0.100                 | 0.20                  | 150                       | 200         |

| +3.3 Vaux     | 0.375                 | 1.10                  | 150                       | 5000        |

| +1.5 VIO      | 1.500                 | 4.00                  | 150                       | 200         |

#### +3.3-V Supply

## Overload Trip Point with MISET = 6.04 $k\Omega$

Desired I<sub>TRIP</sub> (nom) ≅ 10 A

$$R_{SENSE} = \frac{V_{RTRIP\;(nom)}}{I_{TRIP\;(nom)}} = \frac{63\;mV}{10\;A} = 0.0063\;\Omega \quad \therefore Choose\;6\;m\Omega,\;2\%\;sense\;resistor$$

$$I_{TRIP(min)} = \frac{V_{TRIP (min)}}{R_{SENSE (max)}} = \frac{48 \text{ mV}}{6.12 \text{ m}\Omega} = 7.84 \text{ A}$$

$$I_{TRIP(max)} = \frac{V_{TRIP (max)}}{R_{SENSE (min)}} = \frac{76 \text{ mV}}{5.88 \text{ m}\Omega} = 12.93 \text{ A}$$

#### +5-V Supply

## Overload Trip Point with MISET = 6.04 $k\Omega$

Desired  $I_{TRIP}$  (nom)  $\cong$  7 A

$$R_{\text{SENSE}} = \frac{V_{\text{RTRIP (nom)}}}{I_{\text{TRIP (nom)}}} = \frac{53 \text{ mV}}{7 \text{ A}} = 0.00589 \ \Omega \quad \therefore \text{Choose 6 m} \Omega, \ 2\% \text{ sense resistor}.$$

$$I_{TRIP(min)} = \frac{V_{TRIP (min)}}{R_{SENSE (max)}} = \frac{43 \text{ mV}}{6.12 \text{ m}\Omega} = 7.03 \text{ A}$$

$$I_{TRIP(max)} = \frac{V_{TRIP (max)}}{R_{SENSE (min)}} = \frac{63 \text{ mV}}{5.88 \text{ m}\Omega} = 10.71 \text{ A}$$

## 3.3 Volt or 1.55 Volt Supply for V<sub>IO</sub>

Overload trip point with MISET = 6.04  $k\Omega$ .

Desired

$$I_{TRIP(nom)} = 4 A$$

$$R_{SENSE} = \frac{V_{TRIP(nom)}}{I_{TRIP(nom)}} = \frac{23.5 \text{ mV}}{4.0 \text{ A}} = 0.00598\Omega$$

Choose 0.006  $\Omega$

$$I_{TRIP(min)} = \frac{20 \text{ mV}}{0.00612 \Omega} = 3.27 \text{ A}_{MIN}$$

$$I_{TRIP(max)} = \frac{27 \text{ mV}}{0.00588 \Omega} = 4.594 \text{ A}_{MIN}$$

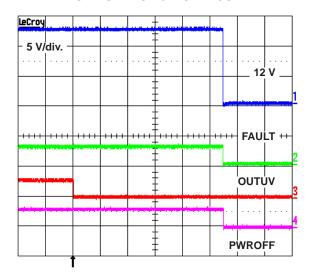

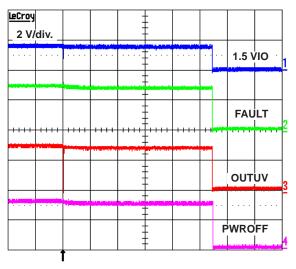

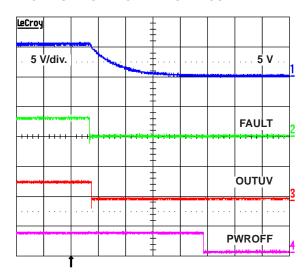

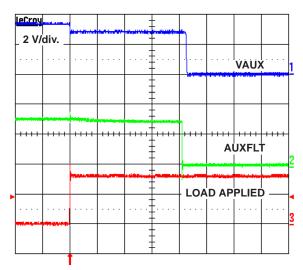

#### **Thermal Shutdown**